The world’s Largest Sharp Brain Virtual Experts Marketplace Just a click Away

Levels Tought:

Elementary,Middle School,High School,College,University,PHD

| Teaching Since: | May 2017 |

| Last Sign in: | 408 Weeks Ago, 3 Days Ago |

| Questions Answered: | 66690 |

| Tutorials Posted: | 66688 |

MCS,PHD

Argosy University/ Phoniex University/

Nov-2005 - Oct-2011

Professor

Phoniex University

Oct-2001 - Nov-2016

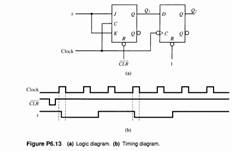

The circuit of Fig. P6.13a contains a JK flip-flop and a D flip-flop. Complete the timing diagram of Fig. P6.13b by drawing the waveforms of signals Q1. and Q2, assuming that:

(a) The 1K flip-flop is negative edge triggered.

(b) The 1K flip-flop has data lockout.

Hel-----------lo -----------Sir-----------/Ma-----------dam-----------Tha-----------nk -----------You----------- fo-----------r u-----------sin-----------g o-----------ur -----------web-----------sit-----------e a-----------nd -----------acq-----------uis-----------iti-----------on -----------of -----------my -----------pos-----------ted----------- so-----------lut-----------ion-----------.Pl-----------eas-----------e p-----------ing----------- me----------- on-----------cha-----------t I----------- am----------- on-----------lin-----------e o-----------r i-----------nbo-----------x m-----------e a----------- me-----------ssa-----------ge -----------I w-----------ill----------- be-----------